| Version 21 (modified by , 13 years ago) ( diff ) |

|---|

Build Framework

Once app_sub.ngc has been copied to current ISE project folder, we are ready to build the framework and generate a bit file for FPGA download.

Perform following operations :

- Start Xilinx ISE

- Open CRKit project located at

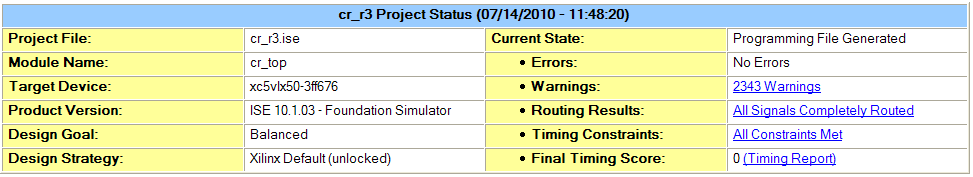

d:\hw\cr_build\cr_r3_sim\cr_r3.ise. The opened project should look like as shown in Figure 1.

- You have the option to re-synthesize the framework. Note the application module e.g. app_sub.ngc is not synthesized at this stage, this has been done within MATLAB/Simulink. To synthesize the framework, right-click on Synthesize - XST in processes window, and select run or re-run. This step can be skipped if you already have synthesized the framework at an earlier stage, hence save some build time.

- Proceed with the place/route stage. Right-click on Implement Design in processes window, and select run or re-run. Once this step is completed succesfully, you should see All Signals Completely Routed and All Constraints Met under the project status as shown in Figure 2.

- Generate bit file. Right-click on Generate Programming File in processes window, and select run or re-run. Once this step is done, the bit file is available at

d:\hw\cr_build\cr_r3_sim\cr_top.bit.

- Use Xilinx Impact tool to download the bit file onto the FPGA.

- FPGA is ready to transmit/receive Ehernet packets to/from host. Use your own host software application to do so. However, we do have a Visual Studio based software available on CRKit svn.

Attachments (2)

- ise.png (120.0 KB ) - added by 13 years ago.

- ise_status.png (13.4 KB ) - added by 13 years ago.

Download all attachments as: .zip

Note:

See TracWiki

for help on using the wiki.