| Version 5 (modified by , 10 years ago) ( diff ) |

|---|

FPGA Components

Table of Contents

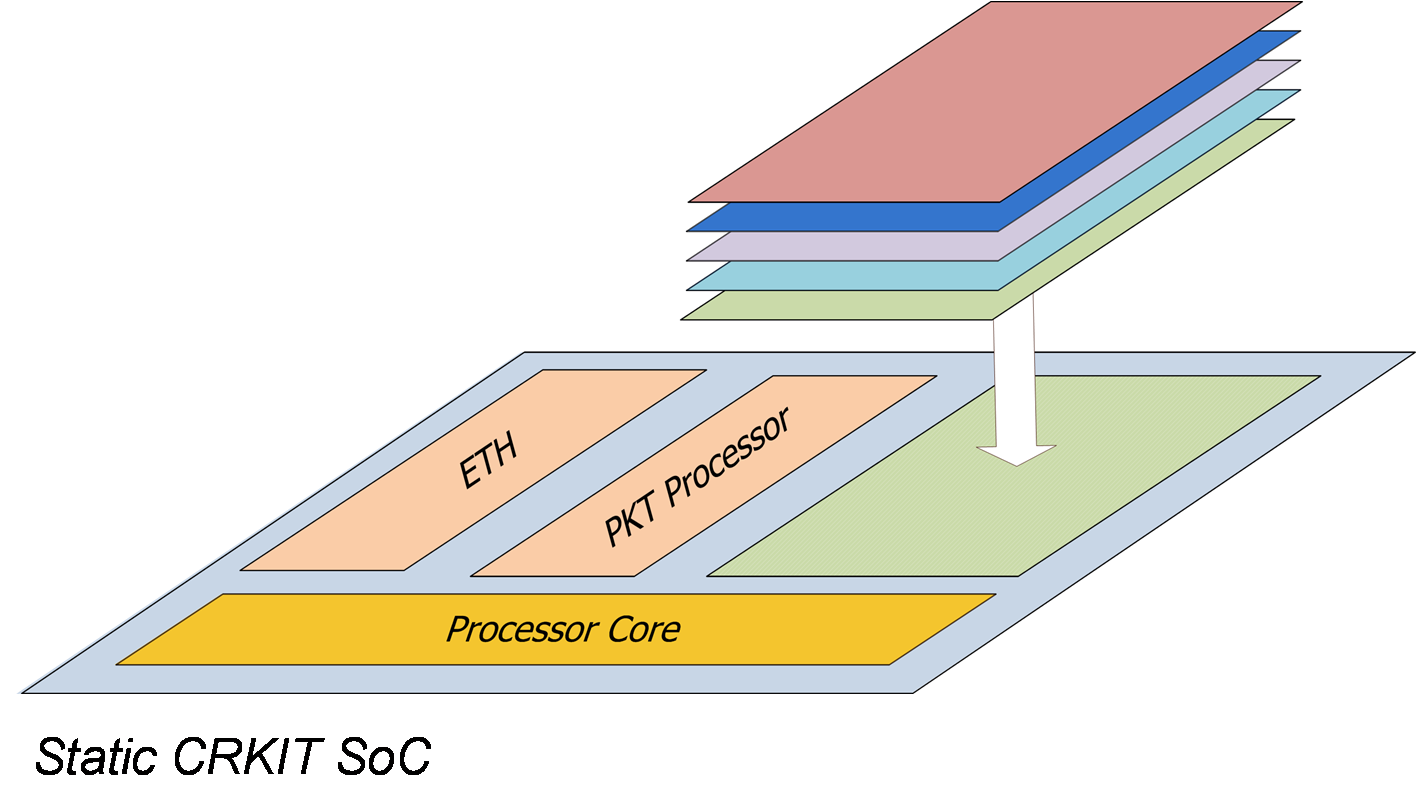

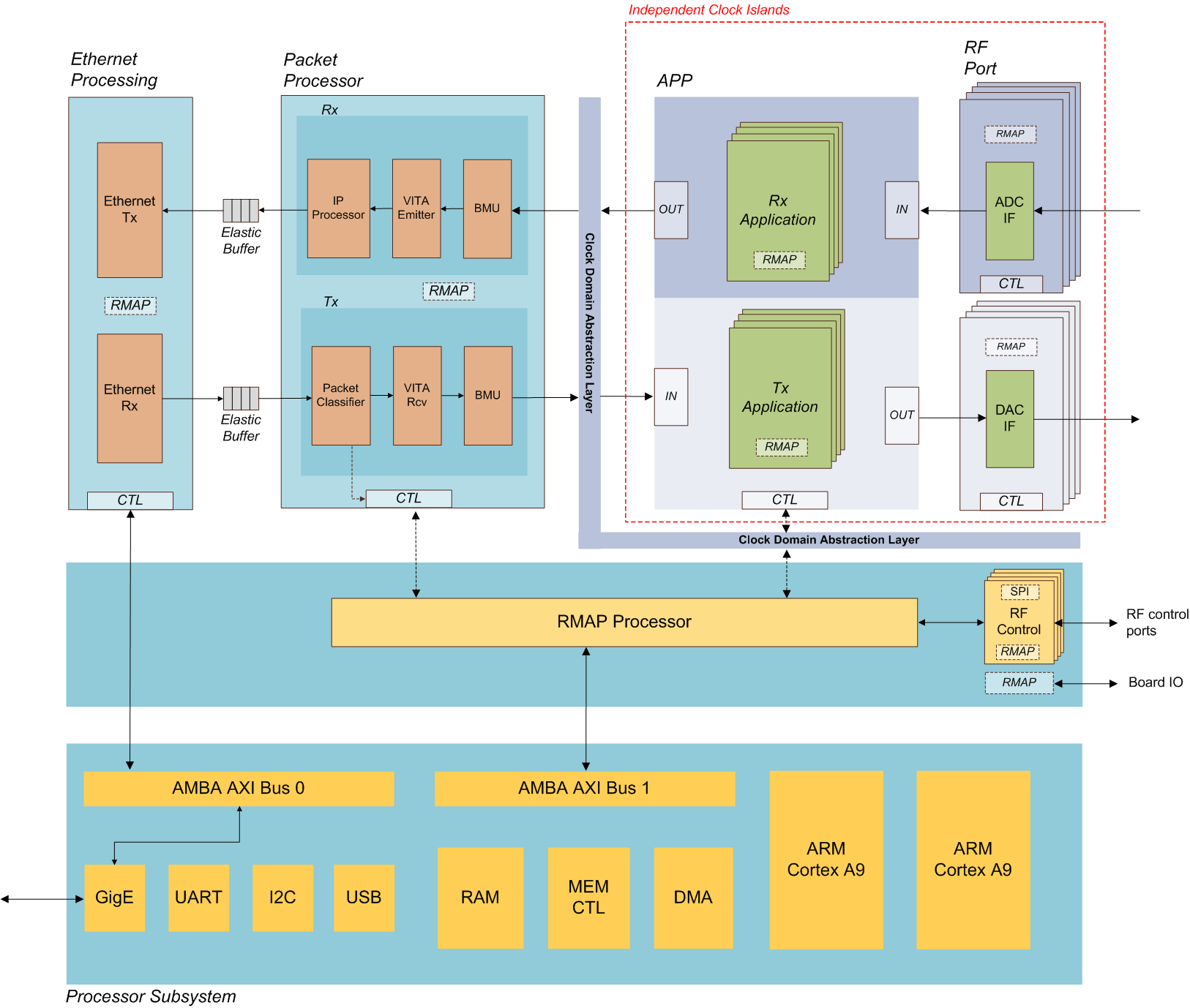

FPGA design part of the WiSer framework aims at supporting multiple hardware platforms where different communication centric applications can be dynamically linked. The FPGA framework hence provides a static part that is platform specific, and a set of dynamic apps can be instantiated by the developer onto this static part to enable specific functions for the cognitive radio application space.

FPGA framework architecture for Zynq based platforms is as shown below. Main blocks of the framework are 1) Processor subsystem - Signle ARM Cortex A9 core is being used with dual AXI bus architecture, AXI0 for Ehternet/IP packet traffic, and AXI1 for all the other data such as hardware configuration, system control and monitoring. 2) Ethernet processing - provides Ethernet packing/unpacking functionality, and integrating with A

Attachments (2)

-

fig01_dyn_app.png

(157.1 KB

) - added by 10 years ago.

Dynamic CR apps

-

fig01_framework.png

(126.7 KB

) - added by 10 years ago.

framework_r5

Download all attachments as: .zip